Микропроцессоры архитектуры SPARC

Масштабируемая процессорная архитектура SPARC (Scalable Processor Architecture) разработана компанией Sun Microsystems в 1986 году. Архитектура SPARC – это архитектура системы команд центрального процессора, полученная на основе понятия о вычислительной машине с ограниченным набором команд RISC (Restricted (Reduced) Instruction Set Computer). Микропроцессоры архитектуры SPARC лицензированы и изготавливаются по спецификациям Sun несколькими производителями, в том числе ЗАО «МЦСТ».

Первоначально архитектура SPARC была разработана с целью упрощения реализации 32-битового процессора и получила название SPARC V7. Она обладала всеми чертами классических RISC процессоров, сочетая простоту набора команд и высокую скорость исполнения кода. Впоследствии, по мере улучшения технологии изготовления интегральных схем, она постепенно развивалась и в 1990 году опубликована спецификация SPARC V8, а затем, в 1993 году – 64-битовая версия архитектуры (SPARC V9), положенная в основу новых микропроцессоров, получивших название UltraSPARC.

Процессоры архитектуры SPARC V8 (МЦСТ R150 и МЦСТ R500) – первые продукты ЗАО «МЦСТ». Благодаря надёжности, стабильной производительности и умеренному энергопотреблению они хорошо зарекомендовали себя в различных управляющих комплексах.

В настоящее время завершена разработка микропроцессора МЦСТ R1000, совместимого с архитектурой SPARC V9. Характеристики R1000 допускают его применение как в системах управления, так и при решении задач обработки данных.

Рассмотрим основные свойства архитектуры SPARC на примере микропроцессора МЦСТ R500. В соответствии со спецификацией SPARC V8 микропроцессор характеризуется следующими свойствами:

- линейное 32-разрядное адресное пространство, т.е. пронумерованная последовательность ячеек памяти от минимального номера до максимального (0х00000000…0хFFFFFFFF – адресация до 4 Гбайт оперативной памяти);

- небольшое количество простых форматов 32-разрядных команд. Все команды в памяти выровнены по границе 32-разрядных слов. Имеется всего три базовых формата команд, в которых поля кода операции и регистровых операндов всегда находятся в одних и тех же разрядах. Доступ к памяти и ввод/вывод могут осуществляться только командами чтения/записи;

- небольшое количество способов адресации – адрес по памяти вычисляется либо как «регистр + регистр», либо как «регистр + непосредственное значение»;

- трёхадресная регистровая команда – команды большей частью выполняют действия с двумя операндами (двумя регистрами или одним регистром и константой), помещая результат в третий регистр;

- 136-регистровый файл с 8 окнами по 16 регистров и окном из 8 глобальных регистров. В каждый отдельный момент времени программа «видит» 8 глобальных целочисленных регистров, 16-регистровое текущее окно и 8 регистров из окна предыдущей процедуры. Регистровое окно может трактоваться как способ ускоренного доступа к параметрам процедуры, локальным значениям и адресам возврата;

- отдельный регистровый файл вещественных регистров. В программах файл может трактоваться как набор из 32 регистров обычной точности (32-разрядных), или 16 регистров двойной точности (64-разрядных), или 8 регистров учетверённой точности (128-разрядных), или как смесь тех или иных;

- отложенная передача управления – процессор всегда выбирает команду, следующую за командой отложенной передачи управления. Эта команда может быть выполнена или не выполнена в зависимости от состояния «аннулирующего» разряда в команде передачи управления;

- быстрые обработчики прерываний – прерывания собраны в линейную таблицу, их генерация приводит к созданию в регистровом файле нового регистрового окна.

- тегированные команды – команды тегированного сложения / вычитания рассматривают два младших разряда своих операндов в качестве тегов;

- команды межпроцессорной синхронизации – одна команда выполняет непрерываемую операцию «чтения и последующей записи», другая – непрерываемый «обмен содержимого регистра и памяти».

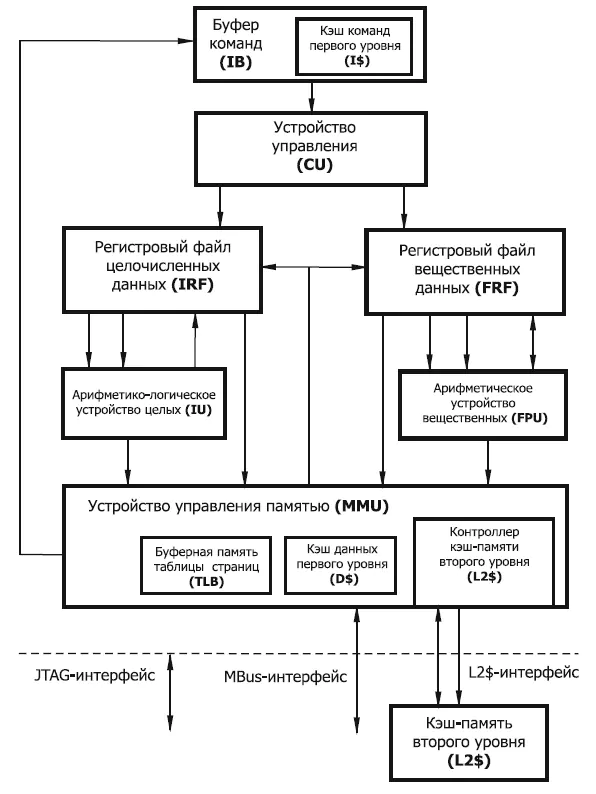

Рассмотрим структуру ядра процессора МЦСТ R500, приведённую на рисунке 1, и основные функции элементов ядра.

Рисунок 1 – Структура ядра микропроцессора МЦСТ R500

Буфер команд (IB). Данный модуль предназначен для выдачи запросов на получение команд в устройство управления памятью, приёма, промежуточного хранения и выдачи команд в устройство управления. Одним из основных компонентов буфера команд является кэш-память команд первого уровня.

Кэш команд первого уровня (I$). Кэш-память – высокоскоростная память небольшого объёма с низкой задержкой доступа, предназначенная для ускорения обращения к часто используемым блокам основной оперативной памяти. Ёмкость кэша I$ составляет 16 Кбайт. В кэш команд входит три блока памяти: память данных, память тегов и память механизма старения. Механизм старения определяет, какие блоки в памяти данных могут быть замещены. Кэш I$ встроен в ядро и находится на том же кристалле.

Устройство управления (CU) предназначено для решения следующих задач:

- дешифрирование поступающих из кэша команд I$ инструкций;

- формирование пусков и блокировки устройств;

- организация чтения операндов из целочисленного IRF и вещественного FRF регистровых файлов для соответствующих арифметико-логических устройств (АЛУ) и записи результатов в соответствующие регистровые файлы;

- управление байпасами устройства целочисленных команд.

Байпас (англ. bypass – обход) – функция в электронном устройстве, позволяющая выполнить коммутацию входного сигнала непосредственно на выход, минуя все функциональные блоки. При проектировании суперскалярных процессоров байпасы применяют для сокращения количества блокировок вычислительного конвейера (см. ниже), обходя избыточные элементы на пути доставки данных. Если выход одной из стадий конвейера требуется на вход другой стадии, данные передаются через байпас-шину. Без байпасов данные пришлось бы записывать и считывать из регистрового файла. Это может потребовать исполнения дополнительных стадий конвейера и вызовет замедление.

Устройство CU содержит регистры состояния процессора и организует их запись, чтение и модификацию. Кроме того, оно управляет обработкой программных и аппаратных исключительных ситуаций и внешних прерываний.

Регистровый файл – модуль микропроцессора, реализующий его регистры в виде массива запоминающих ячеек. В ядре процессора R500 находятся 2 регистровых файла: для целочисленных данных и для вещественных данных.

Регистровый файл целочисленных данных (IRF). В IRF хранятся данные целочисленного типа для проведения с ними операций. Регистровый файл содержит 136 регистров по 32 бита (8 окон по 16 регистров и 1 окно из 8 глобальных регистров).

Регистровый файл вещественных данных (FRF). В этом модуле хранятся данные вещественного типа. Регистровый файл FRF содержит 32 регистра 32-разрядных данных. При этом модуль может трактоваться в программах как набор из 32 регистров одинарного формата (разрядность 32 бита), либо как 16 регистров двойного формата (разрядность 64 бита), либо как смешанный набор регистров первого и второго вида.

Арифметико-логическое устройство целочисленных команд (IU) предназначено для выполнения команд целочисленного сложения/вычитания, логических команд, команд сдвига, а также вычисления адреса в командах обращения к памяти и передачи управления.

Арифметико-логическое устройство вещественных команд (FPU) предназначено для выполнения команд с операциями над вещественными числами, а также команд умножения и деления целых чисел.

Устройство управления памятью (MMU) выполняет следующие функции:

- Определяет множество адресных контекстов, которые соответствуют программным процессам. Адресный контекст процесса включает в себя содержимое выделенного процессу адресного пространства задачи, а также содержимое относящихся к процессу аппаратных регистров и структур данных ядра. Адреса в адресных контекстах уникальны.

- Преобразует 32-разрядные виртуальные адреса активных процессов в 36-разрядные физические адреса оперативной памяти. Соответствие виртуальной памяти физической обеспечивается для страниц размером 4 Кбайт, сегментов размером 256 Кбайт, областей размером 16 Мбайт и контекстов размером 4 Гбайт.

- Задаёт совместное использование памяти. Области адресных пространств для пар контекстов могут быть установлены разделяемыми с точностью до страницы.

- Организует защиту памяти. Доступ к адресуемой памяти назначается с установкой ограничений. Каждому контексту можно индивидуально разрешить доступ к страницам по чтению, записи или выполнению.

- Обеспечивает (при программной поддержке со стороны операционной системы) механизм подкачки отсутствующих в основной памяти страниц из внешней памяти.

- Обеспечивает поддержку обращений операционной системы к другим контекстам в специальных режимах и режимах защиты.

В устройство MMU входят кэш таблицы страниц TLB (Table Lookaside Buffer), кэш данных первого уровня D$ (Data Cache) и контроллер кэш-памяти второго уровня L2$ (L2$ controller).

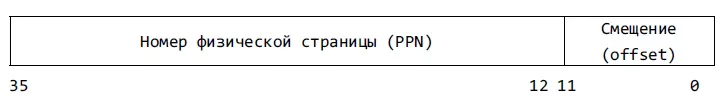

Физические адреса состоят из номера физической страницы PPN (Physical Page Number) и смещения внутри страницы (offset).

Рисунок 2 – Структура физического адреса

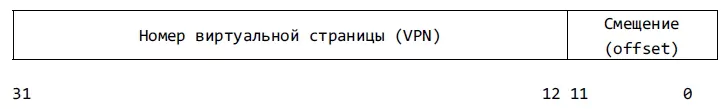

Виртуальные адреса состоят из номера виртуальной страницы VPN (Virtual Page Number) и смещения внутри страницы (offset).

Рисунок 3 – Структура виртуального адреса

Устройство управления памятью выполняет трансляцию адресов путём обращения к древовидной таблице трансляции в оперативной памяти, называемой таблицей страниц PT (Page Table). Когда трансляция установлена, MMU загружает строку таблицы страниц в свой кэш таблицы страниц TLB, чтобы можно было избежать обращения в память к PT при последующих обращениях. Виртуальные адреса, хранимые в кэше TLB, помечаются 16-разрядным номером контекста.

Для оптимизации размещения таблиц страниц в оперативной памяти преобразование адресов выполняется с помощью 4-уровневых таблиц страниц. Такая структура обеспечивает отображение памяти для страниц размером 4 Кбайт.

В микропроцессоре МЦСТ R500 реализован принцип конвейерного выполнения команд. Количество стадий конвейера зависит от типа выполняемой операции.

Команды над целочисленными операндами (целые команды) имеют 5-стадийный конвейер выполнения:

- F (Fetch) – выборка команды из кэша команд I$;

- D (Decode) – дешифрация (декодирование) команды и чтение операндов из регистрового файла целых IRF;

- E (Execute) – выполнение целой команды в АЛУ целых IU;

- C (Cache) – запись результата целой команды в буферный регистр;

- W (Write) – запись результата в целый регистровый файл IRF.

| F | D | E | C | W |

Рисунок 4 – Конвейер целых команд

Конвейер выполнения вещественных команд включает семь стадий:

- F – выборка команды из кэша команд I$;

- D (Decode) – дешифрация команды;

- R (Read) – чтение операндов из вещественного регистрового файла FRF;

- E1, E2, E3 (Execute) – выполнение команды в вещественном АУ FPU;

- W (Write) – запись результата в вещественный регистровый файл FRF.

| F | D | R | E1 | E2 | E3 | W |

Рисунок 5 – Конвейер вещественных команд

Команды загрузки из кэш-памяти первого уровня L1$ имеют 5-стадийный конвейер выполнения

- F – выборка команды из кэша команд I$;

- D (Decode) – дешифрирование команды;

- E (Execute) – вычисление виртуального адреса и обращение в кэш данных первого уровня D$;

- C (Cache) – формирование результата команды загрузки (формирование физического адреса запроса на случай промаха в кэше данных первого уровня D$);

- W (Write) – запись результата в целый регистровый файл IRF.

| F | D | E | C | W |

Рисунок 6 – Конвейер команд загрузки из кэша данных первого уровня D$

Конвейер выполнения команды загрузки из кэш-памяти второго уровня L2$ имеет 14 стадий. Дополнительно к общим стадиям здесь имеются:

- С – формирование физического адреса запроса к кэш-памяти второго уровня L2$;

- C1 – формирование запроса в контроллере кэш-памяти второго уровня L2$;

- C2, С3 – выдача запроса в кэш-память второго уровня L2$;

- C4, С5 – доступ в кэш-память второго уровня L2$;

- C6, С7 – передача тегов и данных из кэш-памяти второго уровня L2$ в микропроцессор;

- C8 – сравнение тегов из кэш-памяти второго уровня L2$ с адресом запроса;

- C9 – формирование результата команды загрузки.

| F | D | E | C | C1 | C2 | C3 | C4 | C5 | C6 | C7 | C8 | C9 | W |

Рисунок 7 – Конвейер команд загрузки из кэш-памяти

В заключение рассмотрим основные особенности архитектуры SPARC V9, на которой реализован микропроцессор МЦСТ R1000:

- Линейное 64-разрядное адресное пространство (позволяет адресовать гипотетически до 16 Эбайт, фактически до 256 Тбайт оперативной памяти).

- Небольшое количество простых форматов 32-разрядных команд. Все команды в памяти выровнены по границе 32-разрядных слов. Доступ к памяти и ввод/вывод могут осуществляться только командами чтения/записи.

- Небольшое количество способов адресации – адрес по памяти вычисляется либо как «регистр + регистр», либо как «регистр + непосредственное значение».

- Трёхадресная регистровая команда – команды большей частью выполняют действия с двумя операндами (двумя регистрами или одним регистром и константой), помещая результат в третий регистр.

- Большой оконный регистровый файл. Может содержать от 64 до 528 64-битных регистров общего назначения, которые делятся на 8 глобальных регистров, 8 альтернативных глобальных регистров и в зависимости от реализации различное количество 16-регистровых наборов. Регистровое окно содержит 8 входных, 8 локальных и 8 выходных регистров. В каждый отдельный момент времени программа «видит» 8 глобальных целочисленных регистров и 24-регистровое окно большого регистрового файла. Регистровое окно может трактоваться как способ ускоренного доступа к параметрам процедуры, локальным значениям и адресам возврата.

- Отдельный регистровый файл вещественных регистров. В программах файл может трактоваться как набор из 32 регистров обычной точности (32-разрядных), или 32 регистров двойной точности (64-разрядных), или 16 регистров учетверённой точности (128-разрядных), или как смесь тех или иных.

- Быстрые обработчики прерываний – прерывания собраны в линейную таблицу, их генерация приводит к созданию в регистровом файле нового регистрового окна.

- Команды межпроцессорной синхронизации – одна команда выполняет непрерываемую операцию «чтения и последующей записи», другая – непрерываемый «обмен содержимого регистра и памяти».

- Предсказанные условные переходы.

- Инструкции удаления условных переходов.

- Аппаратно-реализованный стек прерываний.

- RMO (Relaxed memory order) модель памяти. Это модель памяти слабой консистенции позволяет устройствам планировать доступ к памяти почти в любом порядке, пока программы выдают корректный результат.